ОСВАИВАЕМ ПРОГРАММИРУЕМЫЕ

ЛОГИЧЕСКИЕ МАТРИЦЫ ФИРМЫ –ALTERA.

Абрамов Сергей г. Оренбург

Для большинства радиолюбителей конструкторов занимающихся собственными разработками давно известны и освоены цифровые микросхемы. Многие достаточно давно проектируют свои конструкции на микроконтроллерах так как это в значительной степени уменьшает габариты и улучшает функциональность устройств. Вот только беда в том, что не всё можно построить на основе контроллера. Быстродействующие устройства требующие мгновенной реакции на изменяющиеся входные сигналы построить на микроконтроллере не удастся так как в нём организована поэтапная (конвейерная) обработка команд в результате которых принимается решение о выдаче того или иного сигнала. Поэтому наряду с микроконтроллерами приходится использовать обычную логику, иногда с приличным количеством корпусов. Следствием этого является большое число внешних соединений, сложность конструкции и большие габариты печатных плат, большая длина соединительных проводников, сложность построения устройств с высокой тактовой частотой, низкая надёжность. Решением данной проблемы является использование программируемых логических интегральных схем (ПЛИС), которые представляют собой совокупность некоторого числа функциональных базовых элементов, не имеющих жестких электрических соединений между собой, что позволяет задавать практически произвольную конфигурацию с целью создания той или иной электронной схемы. На первом этапе ПЛИС представляли собой микросхемы с пережигаемыми перемычками такие как К556РТ4-РТ5 и др. на них можно было создать некоторые функции но запихнуть небольшую схему со счётчиками и триггерами было не возможно.

Этапы проектирования устройств на основе простой логики плохо автоматизированы и в случае ошибки необходимо дорабатывать плату вводить дополнительные элементы. Изучение программного Пакета MAX+plus II BASELINE и ПЛИС фирмы Altera, позволит не только упростить схему но и не наступать на множество подводных камней. Данное программное обеспечение можно использовать и при проектировании схем на 155серии и её аналогах. Для программирования (создания соединений) в PLD (а также и

CPLD) используются технологии EPROM, EEPROM и FLASH. Для радиолюбителей наибольший интерес представляют микросхемы FLASH так как они позволяют перепрограммировать кристалл порядка 100 раз и после снятия питающего напряжения сохраняют структуру установленную в результате программирования.

В данной статье будут рассмотрены вопросы поэтапной разработки схем на основе ПЛИС фирмы Altera - EPM3064А как наиболее дешёвой. Она размещена в 44 выводном корпусе типа PLCC. Микросхема имеет смешанное питание и мультивольтовый интерфейс ввода/вывода (I/O). Напряжение питания логического ядра 3,3 вольта элементов ввода/вывода – 5; 3,3; и 2,5 вольта. Максимальная тактовая частота 227,3мГц в зависимости от модификации. Установкой битов конфигурации возможно управлять крутизной фронтов (Slew Rate) входных/выходных сигналов. Имеется также реализация выходов с открытым стоком установкой бита (Open Drain). Имеется возможность установить режим энергосбережения который уменьшает более чем на 50% потребляемую мощность. Имеется также возможность установить бит секретности (security bit) который не позволит скопировать внутреннюю конфигурацию микросхемы. Данная микросхема имеет 4 блока логических матриц и 64 макроячейки. Программируемые триггеры макроячеек имеют индивидуальные входы синхронизации (clock), разрешения синхронизации (clock enable), обнуления (clear), и предустановки (preset). Каждая макроячейка может рассматриваться как программируемая матрица И и фиксированная матрица ИЛИ. На выходе матрицы ИЛИ включен регистр с конфигурируемой схемой управления. Схема управления регистром обеспечивает независимо программируемые сигналы синхронизации, разрешения синхронизации, обнуления, и предустановки. В данную микросхему по мнению автора можно запихнуть 10-15 корпусов 155 серии (в продаже имеются микросхемы EPM3256 с 16 блоками логических матриц и 158 выводами).

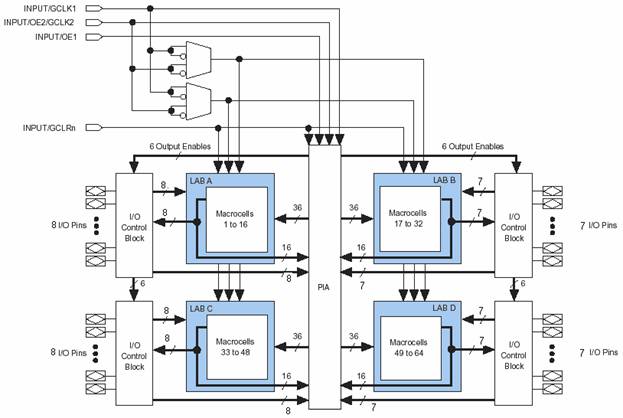

Архитектура EPM3064A включает следующие элементы: Логические блоки (LABs). Макроячейки (Macrocells). Логические расширители, разделяемый (Shareable) и параллельный (Parallel). Программируемая матрица соединений (PIA). Блоки управления вводом/выводом (I/O control blocks). Микросхема имеет четыре специализированных входа (dedicated pin) которые могут использоваться как входы общего назначения или входы высокоскоростных глобальных управляющих сигналов (синхронизации –clock, обнуления clear и двух сигналов разрешения выхода - enable), для каждой макроячейки и контакта ввода вывода. Блок схема изображена на рис1.

Рис1.

Основу архитектуры EPM3064A составляют логические блоки, состоящие из 16 макроячеек. Логические блоки соединяются вместе при помощи программируемой матрицы соединений (PIA). К каждому логическому блоку подводятся следующие сигналы: 36 сигналов от PIA, используемых в качестве логических входов. Глобальные управляющие сигналы. Непосредственные цепи от входных буферов к регистрам, обеспечивающие высокое быстродействие. Подробнее о функциональном составе и принципе работы микросхемы можно почитать в [2].

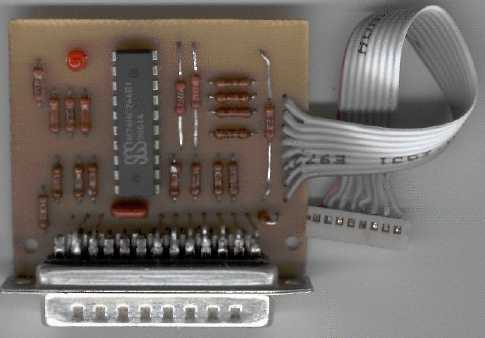

Для программирования микросхемы необходимо изготовить специальный загрузочный

кабель ByteBlasterMV Рис2. Он позволяет быстро и эффективно изменять конфигурацию ПЛИС как в стадии тестирования проекта, так и во время эксплуатации. Перепрограммирование может быть

выполнено непосредственно в системе. Пока идет программирование, выводы

микросхемы переводятся в третье состояние, для избежания

конфликта с системой. Сопротивление внутренних “подтягивающих” резисторов 50 кОм.

Рис2.

Данный загрузочный кабель можно использовать для

программирования микросхем серий МАХ

3000А, МАХ7000, МАХ 9000 а так же многих других, подробнее можно почитать в

[3]. Схема загрузочного кабеля приведена на рис3. Разъём Х1

подключается непосредственно к параллельному порту компьютера или через

удлиняющий кабель причём его длинна не должна превышать

Рис3.

Печатная плата Рис4. изготовлена из одностороннего фольгированного стеклотекстолита толщиной 1,5мм и размерами 52х43мм.

Рис4

Рис4

Для создания проекта в среде системы MAX+PLUS II фирмы

ALTERA необходимо скачать с интернета и установить Рис5.

свободно распространяемый файл baseline10_1.exe

ссылка на сайт приведена в [1]. После установки программы для

полнофункциональной работы необходимо зайти на сайт фирмы Альтера и получить

файл лицензии [4]. На этой странице выбираете ссылку MAX+PLUS II software for students & universities . На следующей

странице выбираете ссылку Version 10.2, 10.1, or 9.23 и нажимаете

кнопку continue. На следующей странице в

окне набираете Ваш регистрационный номер жесткого диска. Для этого в Windows нажимаете кнопку ПУСК

Рис5.

Рис5.

затем Программы, Стандартные, командная строка, и набираете команду dir и enter. Во второй строке распечатается серийный номер диска состоящий из 8 цифр. Вот его и необходимо ввести. Далее нажимаете кнопку continue и на следующей странице заполняете форму. По окончании заполнения формы нажмите кнопку continue. Файл лицензии будет выслан вам по почте. Создайте папку c:\mp2student\ и поместите туда высланный вам файл license.dat. Для установки файла лицензии запустите MAX+plus II 10.1 BASELINE далее нажмите вкладку Options и License Setup в появившемся окне нажмите кнопку Browse, и укажите путь до файла лицензии. Нажмите кнопку OK. После этого все приложения станут доступные. После этого необходимо установить файл драйвера программатора. Для этого нажимаем кнопку ПУСК затем Настройка, панель управления, установка оборудования в появившемся окне нажимаем кнопку далее затем кнопку Да, устройство уже подсоединено и кнопку далее. В следующем окне выбираем Добавление нового устройства и Далее. Устанавливаем кнопку на Установка оборудования выбранного из списка вручную и Далее. В списке выбираем Звуковые, видео и игровые устройства и Далее. Нажимаем кнопку Установить с диска, далее кнопку Обзор. Устанавливаем путь C:\maxplus2\Drivers\win2000 если у вас установлен WindowsXP затем кнопку ОК. Из списка выбираем Altera ByteBlaster, кнопку далее и Готово.

Система MAX+PLUS II имеет средства удобного ввода проекта, компиляции и отладки, а также непосредственного программирования устройств. Программное обеспечение системы MAX+PLUS II содержит 11 приложений и главную управляющую программу. Различные приложения, обеспечивающие создание проекта, могут быть активизированы мгновенно, что позволяет пользователю переключаться между ними щелчком мыши или с помощью команд меню. В это же время может работать одно из фоновых приложений, например, компилятор, симулятор, анализатор синхронизации и программатор.

В

таблице приведено описание приложений.

Таблица

|

Приложение |

Выполняемая функция |

|

Hierarchy Display |

Обзор иерархии - отображает текущую иерархичнскую структуру файлов в виде дерева с ветвями,

представляющими собой подпроекты. |

|

Graphic Editor |

Графический редактор - позволяет разрабатывать

схемный логический проект в формате реального отображения на экране. |

|

Symbol Editor |

Символьный редактор - позволяет редактировать

существующие символы и создавать новые. |

|

Text Editor |

Текстовый редактор - позволяет создавать и

редактировать текстовые файлы логического дизайна, написанные на языках AHDL,

VHDL, Verilog HDL. |

|

Waveform Editor |

Сигнальный редактор - выполняет двойную функцию:

инструмент для разработки дизайна и инструмент для ввода тестовых векторов и

наблюдения результатов тестирования. |

|

Floorplan Editor |

Поуровневый

планировщик - позволяет графическими средствами делать назначения

контактам устройства и ресурсов логических элементов. |

|

Compiler |

Компилятор - обрабатывает графические проекты. |

|

Simulator |

Симулятор - позволяет тестировать логические

операции и внутреннюю синхронизацию проектируемой логической цепи. |

|

Timing Analyzer |

Временной анализатор - анализирует работу

проектируемой логической цепи после того, как она была синтезирована и

оптимизирована компилятором. |

|

Programmer |

Программатор - позволяет программировать,

конфигурировать, проводить верификацию и тестировать ПЛИС фирмы ALTERA. |

|

Message Processor |

Генератор сообщений - выдает на экран сообщения об

ошибках, предупреждающие и информационные сообщения. |

Создадим

рабочий каталог в котором будем размещать наш проект C:\ALTERA_WORK\schetchic. Схему можно

описывать на языках AHDL, VHDL, Verilog HDL (для тех кто предпочитает программирование) или графическим

способом (больше подходит для радиолюбителей). Файл проекта — это графический,

текстовый или сигнальный файл, созданный с помощью графического или сигнального

редакторов системы MAX+PLUS II. Этот файл содержит логику для проекта MAX+PLUS

II и компилируется компилятором. Компилятор может

автоматически обрабатывать следующие файлы проекта: графические файлы проекта (.gdf); текстовые файлы проекта на языке AHDL (.tdf); сигнальные файлы проекта (.wdf);

файлы проекта на языке VHDL (.vhd); файлы

проекта на языке Verilog (.v);

схемные файлы OrCAD (.sch);

входные файлы EDIF (edf); файлы формата Xilinx Netlist (.xnf); файлы проекта Altera

(.adf); файлы цифрового автомата (.smf). Вспомогательные файлы — это файлы, связанные с

проектом MAX+PLUS II, но не являющиеся частью его иерархического дерева.

Большинство таких файлов не содержит логики проекта. Некоторые из них создаются

автоматически приложением системы MAX+PLUS II, другие — пользователем.

Примерами вспомогательных файлов являются файлы назначений и конфигурации (.acf), символьные файлы (.sym),

файлы отчета (.rpt) и файлы тестовых векторов

(.vec).

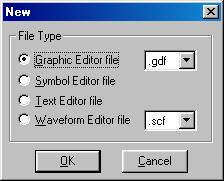

Итак в главном меню нажимаем File затем New и выбираем пункт Graphic

Editor

file и OK рис6. Откроется

окно графического редактора. Далее сохраним наш проект под именем schetchic.gdf в наш каталог C:\ALTERA_WORK\ для этого

нажимаем File затем Save

As

и OK.

Привяжем имя файла к файлу проекта для этого в

главном меню нажимаем File затем Project и далее Set Project to Current File или

вместо этого можно нажать одновременно клавиши Ctrl+Shift+J. Зададим тип микросхемы который будет использоваться в проекте. Для этого

в главном меню нажмем кнопку Assign

затем Device.

В

появившемся окне в строке Device

Familay

выбираем серию MAX3000A. А в окне Devices EPM3064ALC44-4 и OK. Если вы не знаете какой объём у вас будет занимать проект то Devices лучше установить AUTO, компилятор сам подберёт тип микросхемы.

Рис6.

Рис6.

В

рабочей библиотеке имеются элементы различного вида:

1). Логических примитивов (находящихся в папке

c:\maxplus2\max2lib\prim\) таких элементов как and, or, nor и др. с различным количеством входов.

2). Аналогов дискретной логики 74-й серии являющиеся аналогами 155 серии (находящихся в папке c:\maxplus2\max2lib\mf\).

3). Параметризированных логических функций, позволяющих создавать

проекты цифровых устройств любой сложности (находящихся в папке c:\maxplus2\max2lib\mega_lpm\).

Cоздадим

каталог в котором будем размещать собственную библиотеку компонентов C:\ALTERA_WORK\Altera_Lib и подключим

её к проекту. Для этого в главном меню нажмем кнопку Options затем User Libraries и в окно Directory Name введём

путь c:\altera_work\altera_lib затем

OK. Разместить на экране символ можно двумя способами для

этого щелкнем правой кнопкой по месту где хотим

разместить элемент и выберем в появившемся окне менюшку

Enter Symbol в окне Symbol Name

появившегося окна набрать имя элемента и нажать ОК. Или выбрать необходимую библиотеку в окне Symbol Libraries диалогового окна Enter Symbol и

двойным щелчком левой клавиши мыши открыть её. Затем аналогичным образом

выбрать необходимый элемент в окне Symbol File. Если проект небольшой и вас устраивают все элементы находящиеся в библиотеке то таким образом

устанавливаем все необходимые элементы и соединяем их выводы при помощи

проводников. Для этого в графическом редакторе слева находятся пиктограммы при

нажатии на которые можно получить соединение прямая линия, линии размещённые

под прямым углом, сектора и окружности

![]() .Если линия выделена

красным цветом то на ней можно нанести адрес соединения а само соединение не

делать. Входные и выходные цепи наносят выбрав в

библиотеке элементов input и output (при необходимости присваиваем им имя). Для нанесения

логической единицы и нуля набираем vcc или gnd. А если необходим свой символ то необходимо открыть новое

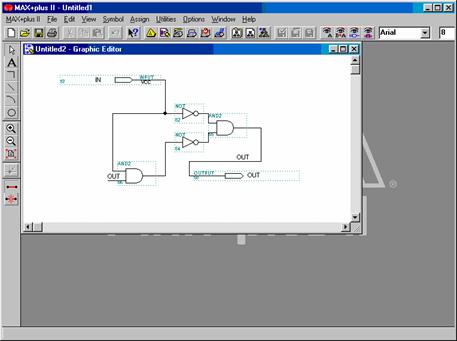

окно графического редактора и нарисовать схему компонента Рис7

присвоить ему имя и сохранить в библиотеке c:\altera_work\altera_lib. Привязать к файлу проекта и откомпилировать нажав ctrl+L. Если

ошибок нет, то можно проверить работу

.Если линия выделена

красным цветом то на ней можно нанести адрес соединения а само соединение не

делать. Входные и выходные цепи наносят выбрав в

библиотеке элементов input и output (при необходимости присваиваем им имя). Для нанесения

логической единицы и нуля набираем vcc или gnd. А если необходим свой символ то необходимо открыть новое

окно графического редактора и нарисовать схему компонента Рис7

присвоить ему имя и сохранить в библиотеке c:\altera_work\altera_lib. Привязать к файлу проекта и откомпилировать нажав ctrl+L. Если

ошибок нет, то можно проверить работу

Рис7

Рис7

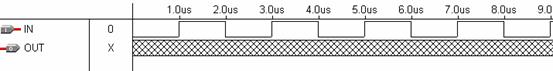

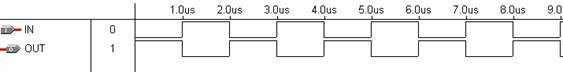

схемы при помощи симулятора. Для этого открываем Waveform Editor, сохраняем файл под

тем же именем. На первой строчке под Name: щёлкаем правой

кнопкой мышки, и выбираем меню Enter nodes from SNF, в появившемся окне

нажимаем кнопку List, в окне Available Nodes & Groups появятся

все входы и выходы нашей схемы. Выделяем необходимые (в данном случае IN и OUT) и нажимаем кнопку => выделенные символы

скопируются в правое окно. Нажимаем OK. В редакторе можно увидеть осциллограмму Рис8. Под именем Value можно установить первоначальное состояние

входного сигнала для этого левой кнопкой мышки щелкаем по строке слева,

в редакторе высвечиваются пиктограммы логической 1 и 0, нажатием пиктограммы

присваиваем состояние входа. Можно ввести изменяющийся во времени сигнал или Z состояние. Конечное время осциллограммы можно ввести зайдя в меню File затем End Time. Метки времени устанавливаются через меню Options затем Grig Size.

Рис8

Рис8

Для

просмотра состояния осциллограммы во времени, запустим Simulator нажав кнопки Ctrl+Shift+L. Осциллограмму можно увидеть на Рис9. Если полученная модель компонента

нас устраивает нарисуем изображение символа. Для этого

откроем редактор символа, в главном меню нажимаем File затем New и

выбираем пункт Symbol Editor file и OK рис6.

Нажав левую кнопку мышки рисуем очертание символа

предварительно выбрав

Рис9

Рис9

слева

в пиктограмме инструмент для рисования. Двойным щелчком левой кнопки мышки открываем меню Enter Pinstub слева в окне указываем тип вывода вход или выход I/O Type. В окне Full Pinstub

Name

Указываем имя вывода (в

нашем случае IN-вход

OUT-выход). Размеры всех линий и надписей

можно изменять и перемещать щёлкнув левой кнопкой по

перемещаемому элементу. Файл необходимо сохранить под тем же именем что и файл

графического редактора в нашу папку библиотеки.

Закрыв

все вспомогательные окна можно ввести символ в файл нашего проекта.

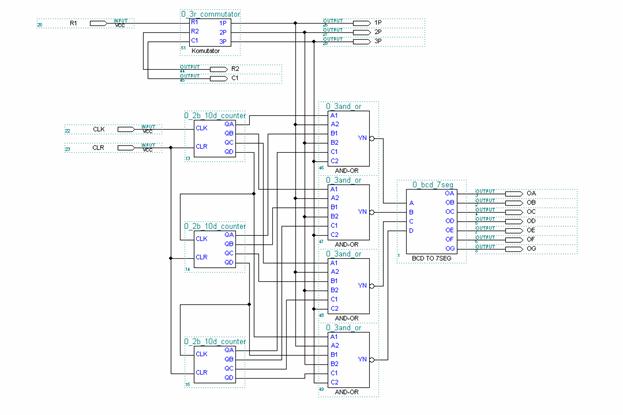

Рассмотрим практическую схему

трёхразрядного счётчика с динамической индикацией Рис10. Блок питания собран на

микросхеме D2

типа LM317 и обеспечивает

Рис10.

необходимое

для D1 напряжение.

Выходной ток разрядов индикатора может быть порядка 80 ма

при всех включенных индикаторах, поэтому разряды индикаторов коммутируются

транзисторами VT1-VT3. Для экспериментальной модели выбрана

схема внутреннего генератора, внешние цепи которого представляют собой

резисторы R16,R18,C2, но в рабочей схеме генератор лучше

делать внешним. По мнению автора ПЛИС не очень хорошо

работают с ёмкостными нагрузками. Разъём Х1 необходим

для подключения к программатору.

Рассмотрим

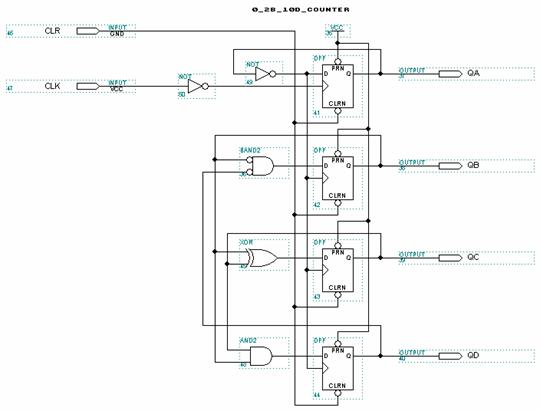

внутреннюю структуру проекта Рис11. Все компоненты создавались заново, по

приведённой выше методике и сохранялись в собственной библиотеке компонентов.

Рис11.

Рис11.

На

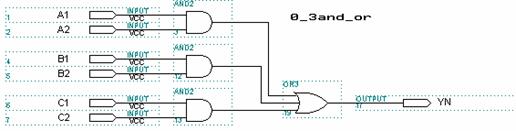

схеме компонент 0_3r_commutator –

это трёхразрядный коммутатор который переключает по

очереди разряды индикатора а также выдаёт управляющие уровни на мультиплексоры 0_3and_or.

Мультиплексоры подключают в зависимости от индицируемого разряда десятичные

счётчики 0_2b_10d_counter к двоично - семисегментному дешифратору 0_bcd_7seg. В названиях компонентов присутствует

Рис12

Рис12

предлог

0_ которым мы обозначаем элемент

собственной библиотеки. На схеме в проекте MAX+PLUS II двойным щелчком левой

кнопки мышки по компоненту откроется графический редактор

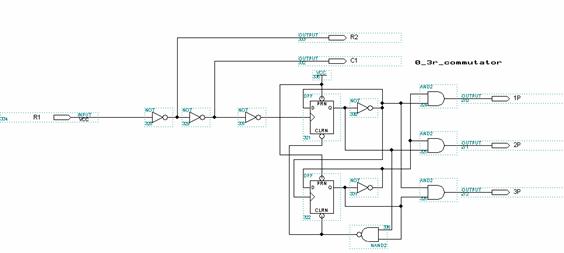

и мы увидим схему элемента. На рис 12 изображен коммутатор,

Рис13.

Рис13.

Рис14.

Рис14.

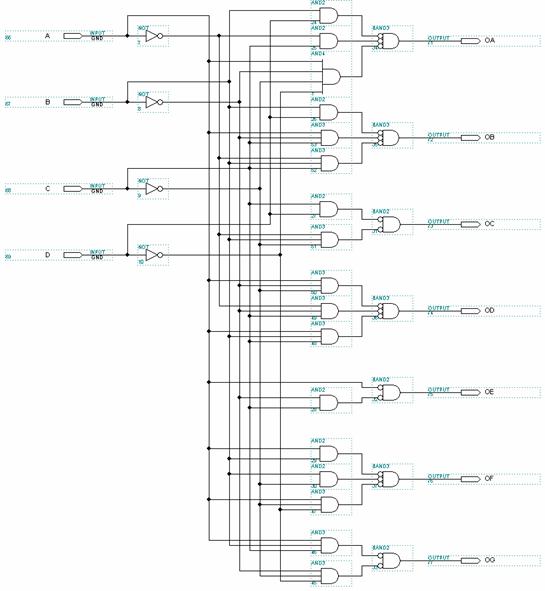

схема которого состоит из примитивов

стандартной библиотеки. Название NOT

–означает инвертор, DFF –D триггер, AND2 – элемент И с двумя

входами. На рис 13 приведена внутренняя схема двоично десятичного

счётчика. На рис 14 мультиплексора. И рис 15 двоично - семисегментного

дешифратора. Ниже приведен список некоторых мегафункций

стандартной библиотеки.

Логические элементы (Gates):

lpm_and – элемент И

lpm_inv – элемент НЕ (инвертор)

lpm_bustri – шина с тремя состояниями

lpm_mux - мультиплексор

lpm_clshift - логический сдвиг

lpm_or – элемент ИЛИ

lpm_constant - константа

lpm_xor – Элемент исключающее ИЛИ

lpm_decode - декодер

mux – мультиплексор

busmux - мультиплексор

Рис15

Рис15

Арифметические компоненты:

divide* - делитель

lpm_compare - компаратор

lpm_abs – абсолютное значение

lpm_counter - счетчик

lpm_add_sub – сумматор/вычитатель

lpm_divide - делитель

lpm_mult - умножитель

Элементы памяти:

altdpram* - двухпортовое ОЗУ

lpm_latch – регистр-защелка

csfifo - FIFO

lpm_shiftreg – сдвиговый регистр

dcfifo* - Dual-Clock FIFO

lpm_ram_dp - двухпортовое ОЗУ

scfifo* - Single-Clock FIFO

lpm_ram_dq – ОЗУ с раздельным входным и выходным портом

csdpram - Cycle-Shared Dual-Port

lpm_ram_io - ОЗУ с общим входным и выходным портом

lpm_ff - Триггер

lpm_rom - ПЗУ

lpm_fifo - Single-Clock FIFO

lpm_dff* - D – триггер и сдвиговый регистр

lpm_fifo_dc

- Dual-Clock FIFO

lpm_tff* – T -триггер

Другие функции:

clklock - PLL

(Phase-Locked Loop)

pll – детектор фронта импульса

ntsc – генератор видеосигнала NTSC

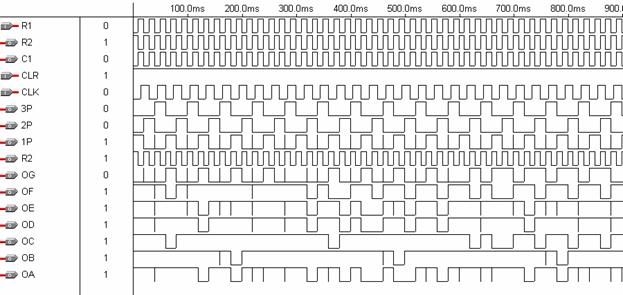

После того как созданы все компоненты,

нарисована общая схема проекта и сделаны все соединения, необходимо сохранить

проект и произвести компиляцию. При отсутствии ошибок необходимо зайти в Waveform Editor и как

было рассмотрено выше

убедиться в правильности работы проекта Рис16.

Рис16.

Разведённая компилятором схема автоматически назначает входные и выходные

ножки это можно посмотреть в Floorplan Editor нажав кнопку

![]() . В этом же редакторе можно изменить назначение ножек по собственному

желанию. Для этого надо нажать кнопку

. В этом же редакторе можно изменить назначение ножек по собственному

желанию. Для этого надо нажать кнопку

![]() и мышью

перетащить имена выводов, отображаемых в окне Unassigned Nodes & Pins,

на соответствующие номера выводов ПЛИС, а затем перекомпилировать проект. После

этого любые изменения, вносимые во внутреннюю структуру проекта, т.е. не

связанные с добавлением или удалением выводов, не будут изменять назначение выводов.

и мышью

перетащить имена выводов, отображаемых в окне Unassigned Nodes & Pins,

на соответствующие номера выводов ПЛИС, а затем перекомпилировать проект. После

этого любые изменения, вносимые во внутреннюю структуру проекта, т.е. не

связанные с добавлением или удалением выводов, не будут изменять назначение выводов.

После этого подключаем схему Рис10 через

разъём Х1 к программатору, а программатор к компьютеру(все

эти процедуры проделываем при выключенном компьютере) подаём питание на схему.

Открываем окно Programmer и нажимаем

кнопку Program. После того как программа зальётся

схема переключится в рабочий режим. Данный способ позволяет менять

внутреннюю схему устройства в зависимости от

изменяющихся задач не переделывая печатной платы.

Не

смотря на кажущуюся сложность изучения

программной среды MAX+PLUS II вы сможете делать проекты гораздо быстрее так как проектирование и отладка на компьютере даёт

больше информации чем изготовление схемы на макетке и

дальнейшее исследование при помощи осциллографа. Как уже отмечалось ранее

полученные результаты можно с успехом использовать при изготовлении конструкций

на основе 155-555 серии.

Ссылки:

1). ftp://ftp.altera.com/pub/software/baseline10_1.exe - Скачать Программу baseline10_1.exe

можно с

сайта -47,1 мб.

2). http://www.altera.ru/cgi-bin/go?44 -Описание семейства MAX 3000

3). http://www.altera.ru/cgi-bin/go?35 - ByteBlasterMV - устройство загрузки

конфигурации ПЛИС фирмы Altera.

4). http://www.altera.com/support/licensing/lic-index.html – Получение файла лицензии.